# A simple Field Programmable Gate Array (FPGA) based high precision low-jitter delay generator

Cite as: Rev. Sci. Instrum. 92, 024701 (2021); https://doi.org/10.1063/5.0030341 Submitted: 23 September 2020 • Accepted: 02 January 2021 • Published Online: 01 February 2021

Zeyang Chen, Xiaohan Wang, Ziwen Zhou, et al.

# **ARTICLES YOU MAY BE INTERESTED IN**

A high-resolution programmable Vernier delay generator based on carry chains in FPGA Review of Scientific Instruments 88, 064703 (2017); https://doi.org/10.1063/1.4985542

A pico-second resolution arbitrary timing generator based on time folding and time interpolating

Review of Scientific Instruments 89, 074701 (2018); https://doi.org/10.1063/1.5037841

A high resolution time-to-digital-convertor based on a carry-chain and DSP48E1 adders in a 28-nm field-programmable-gate-array

Review of Scientific Instruments 91, 024708 (2020); https://doi.org/10.1063/1.5141391

Rev. Sci. Instrum. 92, 024701 (2021); https://doi.org/10.1063/5.0030341 © 2021 Author(s).

# A simple Field Programmable Gate Array (FPGA) based high precision low-jitter delay generator

Cite as: Rev. Sci. Instrum. 92, 024701 (2021); doi: 10.1063/5.0030341 Submitted: 23 September 2020 • Accepted: 2 January 2021 • Published Online: 1 February 2021

Export Citation

Zeyang Chen,<sup>1</sup> Xiaohan Wang,<sup>1</sup> Ziwen Zhou,<sup>1</sup> Ramiro Moro,<sup>1</sup> 🝺 and Lei Ma<sup>1,2,a)</sup> 🝺

# **AFFILIATIONS**

<sup>1</sup>Tianjin International Center for Nanoparticles and Nanosystems, Tianjin University, 92 Weijin Road, Nankai District, Tianjin 300072, China

<sup>2</sup>State Key Laboratory of Precision Measuring Technology and Instruments, Tianjin University, 92 Weijin Road, Nankai District, Tianjin 300072, China

<sup>a)</sup>Author to whom correspondence should be addressed: lei.ma@tju.edu.cn

# ABSTRACT

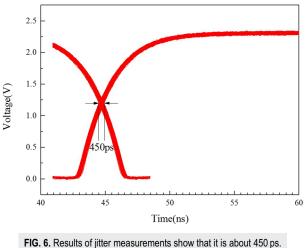

Pulse delay generators are ubiquitous in laboratories to coordinate and control the timing between different devices in applications that include lasers, mass spectrometers, and other scientific instruments. The most important required characteristics are precision, to control time exactly, and low-jitter, to minimize uncertainty in experiments. Here, we introduce a new design of a high precision and low-jitter digital delay generator based on a Field Programmable Gate Array (FPGA). The final delay is composed of steps of 4.2 ns (coarse delay) with fine steps of 16 ps (fine delay). The coarse delay is generated by a 240 MHz pulse sequence from the FPGA with a 50 MHz clock. An embedded time-to-digital conversion unit is used to measure the interval between the external trigger and the clock signal, which, together with an integrated delay generator, is used to realize the fine delay. Jitter compensation is achieved through a measurement-and-feedback module. A computer interface is designed to control the system through a Nios II processor. Measurements confirm a time resolution of  $16 \pm 2$  ps with jitter below  $450 \pm 20$  ps (at  $24 \,^{\circ}$ C) with a maximum delay of 1 s. The whole system is simple in structure and low in cost.

Published under license by AIP Publishing. https://doi.org/10.1063/5.0030341

# I. INTRODUCTION

A digital delay generator (DDG) is a device used to tune the timing between different devices or events, which is widely used in laser systems,<sup>1,2</sup> radar echo signal simulating systems,<sup>3,4</sup> Positron Emission Tomography (PET),<sup>5</sup> Automatic Test Equipment (ATE),<sup>6</sup> time-of-flight mass spectrometers,<sup>7–9</sup> and other wide spectra of scientific instruments.

The operational principle of a DDG is when an external signal triggers the device, an output signal is generated after a digitally set delay. It has been intensively explored in the past several decades, reaching sub-picosecond resolution and jitter.<sup>6,10-13</sup> One recently reported architecture, based on the subset sum delay line (SSDL), achieved a delay accuracy of 76 ps and a dynamic range of 32 ns.<sup>14</sup> Another design, based on the carry chain of Stratix III Field Programmable Gate Array (FPGA), demonstrated a device with a delay accuracy of 38.6 ps.<sup>15</sup> However, with the development of modern experimental requirements, there is urge of a DDG with even higher resolution of picosecond scale, larger time span of seconds, having multiple channels, low cost, and low jitter.<sup>6</sup> The common ways to realize this are the counter method<sup>16</sup> and the delay chip

method.<sup>17</sup> The counter method can provide a wide time range, but its accuracy is limited by the sampling rate, while the delay chip method offers much higher precision; however, it has a far limited range. Aiming for those aforementioned needs, taking advantage of both technologies, the design presented here achieves several tens of picosecond resolution, 1 s of delay range, and more than ten full channels at extremely low cost.

# **II. DESIGN**

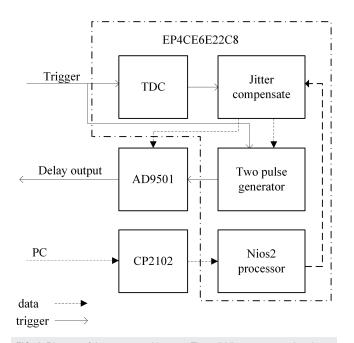

The FPGA chip used here is the EP4CE6E22C8. It has an embedded time-to-digital conversion (TDC) module, two pulse generators, and a Nios II processor with the function of jitter compensation as shown inside the dashed-dotted line in Fig. 1. The total time delay of the DDG is composed of a coarse delay and a fine delay. The coarse delay is realized by using the counter method whose resolution is determined by the sampling rate. The 240 MHz clock signal is generated by multiplication of an external 50 MHz from a crystal oscillator, which is the maximum frequency that the system can run. To generate the fine delay, the coarse delay step is subdivided by the 8-bit control word of the integrated delay generator AD9501, giving

a resolution of 4.2 ns/255 =  $16.5 \text{ ps.}^{18}$  The block diagram of the system is shown in Fig. 1.

After the external trigger enters the system, it splits into two channels: the coarse delay is realized by one channel and the jitter is measured in the other by the TDC. The TDC measures the interval between the trigger and the clock signal and then outputs to the delay compensation module. Through the software interface, the personal computer (PC) sends the user delay setting to a Nios II processor, which will be allotted into coarse delay and fine delay and implemented via a CP2102<sup>24</sup> serial port bridge chip. The processor sends the delay information to the jitter compensation module through the parallel input output (PIO) IP core, which is responsible for processing the delay setting and the measured interval, and further yields the compensated delay consisting of coarse delay and fine delay. The compensated coarse delay will be directly sent to its corresponding module, while the compensated fine delay value is converted into 8 bits, and sent to the AD9501 to synthesize the fine delay. Finally, the delayed signal is output by the AD9501 chip.

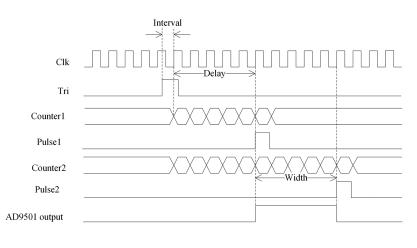

The AD9501 works by comparing the output voltage of a ramp generator against a set DAC value, when they are equal, the delay pulse will be created. Initially, the ramping voltage is set to 0 (reset) by pulling up pin 4. Therefore, the coarse delay module outputs two pulses to the AD9501: one for triggering the fine delay and the other for resetting the ramp generator. The interval setting between these two pulses controls the width of the delay signal. The timing diagram of the module is shown in Fig. 2.

The highest delay resolution in the counter method is determined by the sampling clock frequency. In this design, the 240 MHz clock yields 4.2 ns unit of coarse delay. The time interval between the external trigger and the sampling clock (see Fig. 2) is randomly

**FIG. 1.** Diagram of the system architecture. The solid line represents the trigger signal path, and the dotted line represents the data path. Function blocks inside the dotted-dashed line are the parts of FPGA chip.

distributed from 0 to 1 clock period, which would lead to a jitter of 4.2 ns if no compensation was applied.

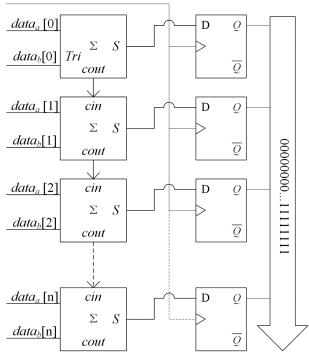

The jitter measurement and compensation module measures the time interval between the trigger and the rising edge of the next clock signal and eliminates the jitter in the output signal. The most commonly used technique for time interval measurement includes current integration,<sup>19–21</sup> counter,<sup>22,23</sup> and time interpolation methods. This last method is realized by inserting much shorter time delay units into the interval and then counting the number of these units until it fills up the full span of the interval. This can be easily implemented in a FPGA and practically not only can improve system integration but also can reduce its cost. The construction of an interpolation circuit is realized simply by using the adder carry chain inside the FPGA<sup>26–30</sup> shown in Fig. 3.

The adder has two n-bit inputs. One is set to all 1 s, while the other has all the high (n - 1) bits at 0, leaving only the lowest bit for the external trigger signal. When the external trigger signal changes to 1, the addition operation is conducted from the lowest significant digit up. Because the lowest adder has its two inputs at 1, a carrier is generated and transferred to the next arithmetic unit for operation, where the inputs are 0 and 1, and a carrier is generated again, and so on. Hence, the pulse signal is transferred upwards in the add carry chain. When the clock signal arrives, the latch of the arithmetic unit locks the result of the adder. A value of 0 in an arithmetic unit indicates that the carrier was generated, and conversely, a value of 1 indicates that the signal did not reach that unit yet. Therefore, the latch locks a column of binary numbers "0000111111," where the position of the 0-1 jump indicates the location of the transmitted signal. Since the time span of each carrier unit is known, the number of zeros in the binary column can be converted to time, which realizes the measurement of the interval between the trigger signal and the clock signal.<sup>31</sup>

The interval measured by the carry-chain needs to be compensated in the total delay by subtracting it from the set delay. First, the delay will be separated into two parts: one is the maximum integer number of coarse delay units that can be fitted in the interval and the other is the reminder, which is less than a coarse delay unit. These two parts are called coarse delay part and the fine delay part, respectively. The realization of the coarse delay is by using the counter method, which is the integer number of fixed unit time of 4.2 ns, as mentioned above; the fine delay is realized by controlling an AD9501 chip through its 8-bit control word and reaches a resolution of 4.2 ns/255. The average length of each arithmetic unit is 0.073 ns,<sup>25</sup> so the time precision of the AD9501 is better than the carry-chain unit. For example, if the measured interval is 0.073 ns, 0.073 ns/0.016 ns  $\approx$  5, so we can compensate the 0.073 ns with 5 units of fine delay that express that interval. After analyzing the delay requirements, the operation is as follows:

- When the coarse delay is set to 0, only the carry-chain would be used to compensate the coarse delay jitter. The pulse delay will only come from the AD9501 with its fine delay.

- (2) When the coarse delay is nonzero, the coarse delay counter kicks-in. The carry-chain will measure the interval between trigger and clock signal, and there would be the following cases:

- (i) If the measured interval "jitter" is less than or equal to the fine delay part, then the output coarse delay part will

# Review of Scientific Instruments

FIG. 2. Timing diagram of the coarse delay module. After the trigger signal arrives, the rising edge of the clock starts Counter1 and Counter2. When the counted value reaches the preset value of Delay, Pulse1 outputs a pulse. When the counted value reaches the preset value of Width, Pulse2 will output a pulse. Pulse1 acts on AD9501 to generate the rising edge of the delay output, and Pulse2 acts on AD9501 to generate the falling edge of the delay output.

**FIG. 4.** Flow chart of the control module. When the serial port receives the data from the PC, it triggers the UART interrupt and enters the processing function, which passes the PC data to each module through PIO.

moved to the fine delay part for subtraction. Since one unit of coarse delay represents 255 units of fine delay, the final output fine delay will be 255 units of fine delay added to the original fine delay minus the "jitter."

Considering both the cost and the simplicity of the system, a Nios II soft core processor was selected. The processor receives the delay set by users from the PC, which then will be sent to the delay module. The performance can be further improved by using the IP core of Qsys. The IP cores that need to be added for data intaking and transmission are Universal Asynchronous Receiver/Transmitter (UART) and PIO. The PC sends the data to the read-register of the UART IP core through CP2102, the rxdata-register of the UART IP core receives the data, enables the read interruption, and assigns the read data to PIO, thus realizing PC's control over the delay system. Figure 4 shows the flow chart of the control module.

**FIG. 3.** Diagram of the interval measurement circuit. All the *data<sub>a</sub>* inputs are set to 1 and all *data<sub>b</sub>* to 0, except for *data<sub>b</sub>*[0], which is connected to the trigger. When the trigger signal (*Tri*) arrives, the adder starts to operate from the least significant digit, outputs the result *S*, and generates the carry out *cout*, which is transmitted to the next carry input *cin*. The next arithmetic unit adds *data<sub>a</sub>* [1], *data<sub>b</sub>* [1], and *cin*, then outputs the result *S*, and generates its own *cout*. This way *Tri* progrades in the carry chain. When the clock rising edge arrives, the result of the arithmetic unit is locked by the latch, and the position reached by *Tri* is recorded in the form of a column of binary numbers.

stay the same, but the fine delay part will be compensated by directly subtracting the "jitter" from the fine delay part.

(ii) If the measured interval "jitter" is greater than the fine delay part, then one coarse delay unit (4.2 ns) will be

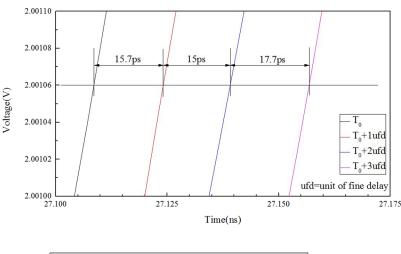

**FIG. 5.** Results of the highest resolution test. From these results, the measured resolution is better than 20 ps and is about 16 ps in average.

# **III. TEST OF PULSE GENERATOR**

To measure the resolution of the DDG, a signal is generated by a DG535 (Stanford Research Systems) and connected to the input of the DDG and also to one channel of an oscilloscope serving as a trigger. Then, the output of the DDG is connected to another channel of the same oscilloscope for measuring. To measure the minimum delay of the output pulse, the oscilloscope display was set to average 4096 shots. Figure 5 shows an example of 3 tests, where 6 units of coarse delay and 126 units of fine delay are set as the reference  $T_0$  with extra 1–3 units of fine time delay. The results of this test indicated that the resolution of DDG is on the order of 16 ps.

In order to measure the jitter, 500 shots were collected in the oscilloscope with fluorescence mode and are presented in Fig. 6. This gives an estimated jitter of 450 ps with the eye figure test, as shown in Fig. 6.

To test the stability of this device, the temperature dependent jitter and resolution measurements have also been conducted, which shows a marginal dependence as 18 ps delay resolution and 458 ps jitter at 53  $^{\circ}$ C compared to the ones shown above at 24  $^{\circ}$ C.

#### **IV. CONCLUSIONS**

This paper presents a new design of a FPGA based low cost delay pulse generator. It seamlessly combines the counter method to generate a coarse delay and an AD9501 for the fine delay, realizing high precision and wide dynamic range with  $16 \pm 2$  ps timing resolution and  $450 \pm 20$  ps jitter. The FPGA adder carry-chain is used to measure the time interval between the external trigger and the sampling clock and effectively reduce the jitter in the final pulse output. The resolution can be further improved by using newer chips with better performance. It can be easily used for a variety of scientific instruments for timing control with very low cost, rather high precision in a compact design.

# ACKNOWLEDGMENTS

This work was supported by the Natural Science Foundation of China under Grant Nos. 17JCZDJC30100 and 11774255.

### DATA AVAILABILITY

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### REFERENCES

<sup>1</sup>J. Junmin, L. Jinyuan, and L. Baiyu, "Research of the new-style digital delay pulse generator in the prototype of laser system," Acta Photonica Sin. **31**, 381–383 (2002).

<sup>2</sup>D. Tian and G. Yang, "Design and development of a miniature digital delay generator for laser-induced breakdown spectroscopy," Instrum. Sci. Technol. 43, 115–124 (2015).

<sup>3</sup>S. Zhaolin, L. Nan, and W. Yinan, "High resolution programmable digital delay generator design and realization," in 2010 International Conference on Intelligent System Design and Engineering Application IEEE Computer Society (IEEE, 2010), pp. 813–816.

<sup>4</sup>L. Hao, "A large dynamic range, high resolution pulse delay circuit design," Dual Use Technol. Prod. **5**, 36–38 (2006).

<sup>5</sup>Y. Liu, H. Li, Y. Wang, T. Xing, H. Baghaei, J. Uribe, R. Farrell, and W.-H. Wong, "A programmable high-resolution ultra-fast delay generator," in 2002 IEEE Nuclear Science Symposium Conference Record, Norfolk, VA, 2002, Vol. 2, pp. 1153–1157.

<sup>6</sup>K. Klepacki, M. Pawłowski, and R. Szplet, "Low-jitter wide-range integrated time interval/delay generator based on combination of period counting and capacitor charging," Rev. Sci. Instrum. 86, 025111 (2015).

<sup>7</sup>C. L. Feng, L. Gao, and J. H. Liu, "Laser mass-spectrometry for online diagnosis of reactive plasmas with many species," Rev. Sci. Instrum. **82**, 063110 (2011).

<sup>8</sup>G. Hui, C. Wentong, and W. Jinxiang, "Application of programmable logic device in multichannel nanosecond digital delay/pulse generator," Anal. Instrum. 3, 13–17 (2002).

<sup>9</sup>S. V. Kovtoun, R. D. English, and R. J. Cotter, "Mass correlated acceleration in a reflectron MALDI TOF mass spectrometer: An approach for enhanced resolution over a broad mass range," J. Am. Soc. Mass Spectrom. 13, 135–143 (2002).

<sup>10</sup>J. P. Martin and K. Ragan, "A programmable nanosecond digital delay and trigger system," in *IEEE Nuclear Science Symposium. Conference Record* (IEEE, 2000), Vol. 2, pp. 12-141–12-144.

<sup>11</sup> H. U. Jang, J. Blieck, G. Veshapidze, M. L. Trachy, and B. D. DePaola, "An autoincrementing nanosecond delay circuit," Rev. Sci. Instrum. **78**(9), 094702 (2007).

<sup>12</sup> J. Kalisz, A. Poniecki, and K. Różyc, "A simple, precise, and low jitter delay/gate generator," Rev. Sci. Instrum. **74**(7), 3507–3509 (2003).

<sup>13</sup>W.-Z. Zhang, X. Qin, L. Wang, Y. Tong, Y. Rui, X. Rong, and J.-F. Du, "A fullyadjustable picosecond resolution arbitrary timing generator based on multi-stage time interpolation," Rev. Sci. Instrum. **90**(11), 114702 (2019).

<sup>14</sup>C. Wang, Y. Chen, J. Huang, and X. Huang, "FPGA-based subset sum delay lines," in 2014 IEEE 23rd Asian Test Symposium (IEEE, Hangzhou, 2014), pp. 287–291.

pp. 287–291. <sup>15</sup>K. Cui, X. Li, and R. Zhu, "High-resolution programmable Vernier delay generator based on carry chains in FPGA," Rev. Sci. Instrum. **88**, 064703 (2017).

<sup>16</sup>L. Peng, "A design of digital delay line based on FPGA," Microcomput. Inf. 26, 132–134 (2010).

<sup>17</sup>Y. X. Ma, "Performance and application of digital delayer AD9501," Electron. Compon. Device Appl. 4, 27–28 (2002).

<sup>18</sup>Model AD 9501, Analogy Devices, Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, USA. <sup>19</sup>T. Ueno, D. Wang, and T. Namihira, "Novel dual marx generator for microplasma applications," IEEE Trans. Plasma Sci. 33, 1205–1209 (2005).

<sup>20</sup> M. Tanaka and H. Ikeda, M. Ikeda, and S. Inaba, "Development of monolithic time-to-amplitude converter for high precision TOF measurement," IEEE Trans. Nucl. Sci. **38**, 301–305 (1991).

<sup>21</sup>A. E. Stevens and R. P. Van Berg, J. Van der Spiegel, and H. H. Williams, "A time-to-voltage converter and analog memory for colliding beam detectors," IEEE J. Solid-State Circuits **24**, 1748–1752 (1989).

<sup>22</sup>D. I. Porat, "Review of sub-nanosecond time-interval measurements," IEEE Trans. Nucl. Sci. 20, 36–51 (1973).

<sup>23</sup>J. Kalisz, "Review of methods for time interval measurements with picosecond resolution," <u>Metrologia</u> 41, 17–32 (2004).

<sup>24</sup>Module CP 2102, Silicon Labs, 2708 Orchard Parkway, San Jose, CA 95134, USA.

<sup>25</sup>Module EP4CE6E22, Intel, 2200 Mission College Blvd, Santa Clara, CA 95054-1549, USA.

<sup>26</sup>J. Song, Q. An, and S. Liu, "A high-resolution time-to-digital converter implemented in field-programmable-gate-arrays," IEEE Trans. Nucl. Sci. 53, 236–241 (2006).

<sup>27</sup>A. M. Amiri, A. Khouas, and M. Boukadoum, "On the timing uncertainty in delay-line-based time measurement applications targeting FPGAs," in *2007 IEEE International Symposium on Circuits and Systems* (IEEE, 2007), pp. 3772–3775.

<sup>28</sup>M. C. Lin, G. R. Tsai, and C. Y. Liu, "FPGA-based high area efficient timeto-digital IP design," in *TENCON 2006—2006 IEEE Region 10 Conference* (IEEE, 2006), pp. 1–4.

<sup>29</sup>S. S. Junnarkar, M. Purschke, and J. F. Pratte, "An FPGA-based, 12-channel TDC and digital signal processing module for the RatCAP scanner," in *IEEE Nuclear Science Symposium Conference Record* (IEEE, 2005), pp. 919–923.

<sup>30</sup>M. D. Fries and J. J. Williams, "High-precision TDC in an FPGA using a 192 MHz quadrature clock," in *2002 IEEE Nuclear Science Symposium Conference Record* (IEEE, 2002), pp. 580–584.

<sup>31</sup>W. Jinyuan and S. Zonghan, "The 10-ps wave union TDC: Improving FPGA TDC resolution beyond its cell delay," in *2008 IEEE Nuclear Science Symposium Conference Record* (IEEE, 2008), pp. 3440–3446.